Intel LE80537GF0414M Arkusz Danych Strona 34

- Strona / 97

- Spis treści

- BOOKMARKI

Oceniono. / 5. Na podstawie oceny klientów

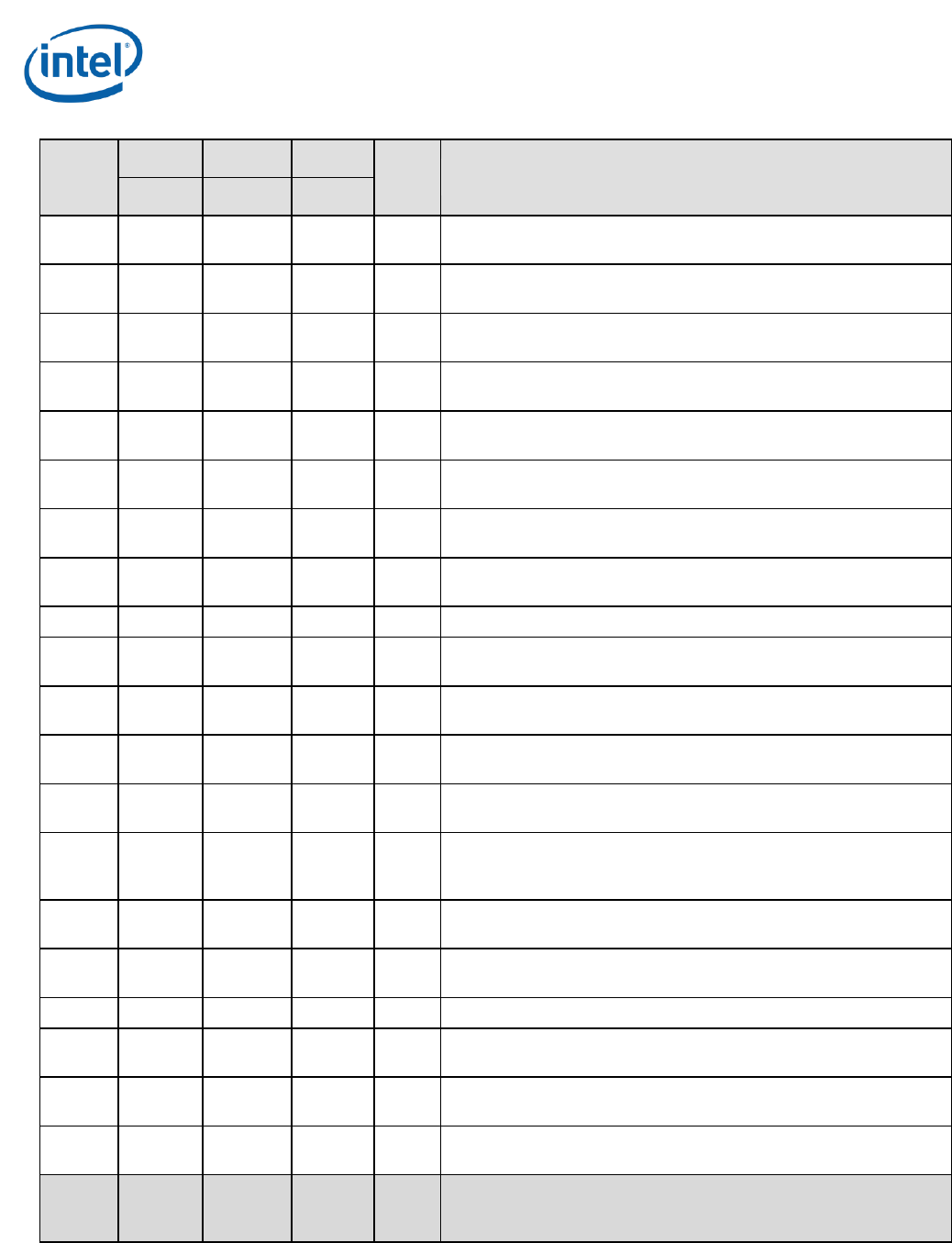

Summary Tables of Changes

34 Specification Update

Number

Stepping

Stepping

Stepping

Plans

ERRATA

E-1

M-1

G-2

AH102

Fixed

Performance Monitoring Event BR_INST_RETIRED May Count

CPUID Instructions as Branches

AH103

X

X

X

No Fix

Performance Monitoring Event MISALIGN_MEM_REF May Over

Count

AH104

X

X

X

No Fix

A REP STOS/MOVS to a MONITOR/MWAIT Address Range May

Prevent Triggering of the Monitoring Hardware

AH105

Fixed

False Level One Data Cache Parity Machine-Check Exceptions May

be Signaled

AH106

X

X

X

No Fix

A Memory Access May Get a Wrong Memory Type Following a #GP

due to WRMSR to an MTRR Mask

AH107

X

X

X

No Fix

PMI While LBR Freeze Enabled May Result in Old/Out-of-date LBR

Information

AH108

X

X

Fixed

Overlap of an Intel

®

VT APIC Access Page in a Guest with the DS

Save Area May Lead to Unpredictable Behavior

AH109

X

X

X

No Fix

VTPR Write Access During Event Delivery May Cause an APIC-

Access VM Exit

AH110

X

X

X

No Fix

BIST Failure After Reset

AH111

X

X

X

No Fix

Performance Monitoring Event FP_MMX_TRANS_TO_MMX May Not

Count Some Transitions

AH112

X

X

X

No Fix

Instruction Fetch May Cause a Livelock during Snoops of the L1

Data Cache

AH113

X

X

X

No Fix

Use of Memory Aliasing with Inconsistent Memory Type may Cause

a System Hang or a Machine Check Exception

AH114

X

X

X

No Fix

A WB Store Following a REP STOS/MOVS or FXSAVE May Lead to

Memory-Ordering Violations

AH115

X

X

X

No Fix

VM Exit with Exit Reason “TPR Below Threshold” Can Cause the

Blocking by MOV/POP SS and Blocking by STI Bits to Be Cleared in

the Guest Interruptibility-State Field

AH116

X

X

X

No Fix

Using Memory Type Aliasing with Cacheable and WC Memory

Types May Lead to Memory Ordering Violations

AH117

X

X

X

No Fix

RSM Instruction Execution under Certain Conditions May Cause

Processor Hang or Unexpected Instruction Execution Results

AH118

X

X

X

No Fix

NMIs may not be blocked by a VM-Entry failure.

AH119

X

X

X

No Fix

Benign Exception after a Double Fault May Not Cause a Triple Fault

Shutdown Problem

AH120

X

X

X

No Fix

IA32_MC1_STATUS MSR Bit[60] Does Not Reflect Machine Check

Error Reporting Enable Correctly

AH121

X

X

X

No Fix

Corruption of CS Segment Register During RSM While Transitioning

From Real Mode to Protected Mode

AH122

X

X

X

No Fix

FP Data Operand Pointer May Be Incorrectly Calculated After an FP

Access Which Wraps a 4-Gbyte Boundary in Code That Uses 32-Bit

Address Size in 64-bit Mode

- Including Intel 1

- Specification Update 2

- Contents 3

- Revision History 4

- 6 Specification Update 6

- Preface 7

- Nomenclature 8

- Specification Update 9 9

- Identification Information 10

- Table 3. Intel 13

- 945 Express Chipset Family 13

- Component Markings 13

- 14 Specification Update 14

- Table 2. Intel 14

- 965 Express Chipset Family 14

- 16 Specification Update 16

- Table 1. Intel 17

- Celeron 17

- 18 Specification Update 18

- Summary Tables of Changes 19

- Specification Update 21 21

- Errata for Intel 22

- 24 Specification Update 24

- 26 Specification Update 26

- 28 Specification Update 28

- Based on Mobile Intel 29

- 30 Specification Update 30

- 32 Specification Update 32

- 34 Specification Update 34

- 38 Specification Update 38

- May Terminate Early 38

- 40 Specification Update 40

- Specification Update 43 43

- Specification Update 45 45

- Not Be Accurate 46

- Specification 47

- Address Translations 47

- Specification Update 49 49

- Specification Update 51 51

- Invocation 52

- Specification Update 53 53

- Be Incorrect 54

- Specification Update 55 55

- Specification Update 57 57

- Accurate 59

- Specification Update 61 61

- Specification Update 63 63

- Shootdown 65

- Specification Update 67 67

- Address 68

- IA32_DEBUGCTL[12] Is Set 69

- Software Interrupts 71

- Specification Update 73 73

- Specification Update 75 75

- Specification Update 77 77

- Specification Update 79 79

- Instructions as Branches 81

- Signaled 82

- Information 83

- AH108. Overlap of an Intel 84

- VM Exit 84

- Count Some Transitions 85

- Memory-Ordering Violations 86

- Specification Update 87 87

- Shutdown 88

- Specification Update 89 89

- 90 Specification Update 90

- Erratum Affecting Only Intel 91

- Core™2 Duo Mobile 91

- Processors on Mobile Intel 91

- Be Able to Enter Intel 92

- Enhanced Deeper Sleep 92

- AH6P Activation of Intel 93

- Dynamic 93

- Specification Changes 94

- Specification Update 95 95

- Specification Clarifications 96

- Documentation Changes 97

(100 strony)

(100 strony)

Komentarze do niniejszej Instrukcji