Intel LE80537GF0414M Arkusz Danych Strona 32

- Strona / 97

- Spis treści

- BOOKMARKI

Oceniono. / 5. Na podstawie oceny klientów

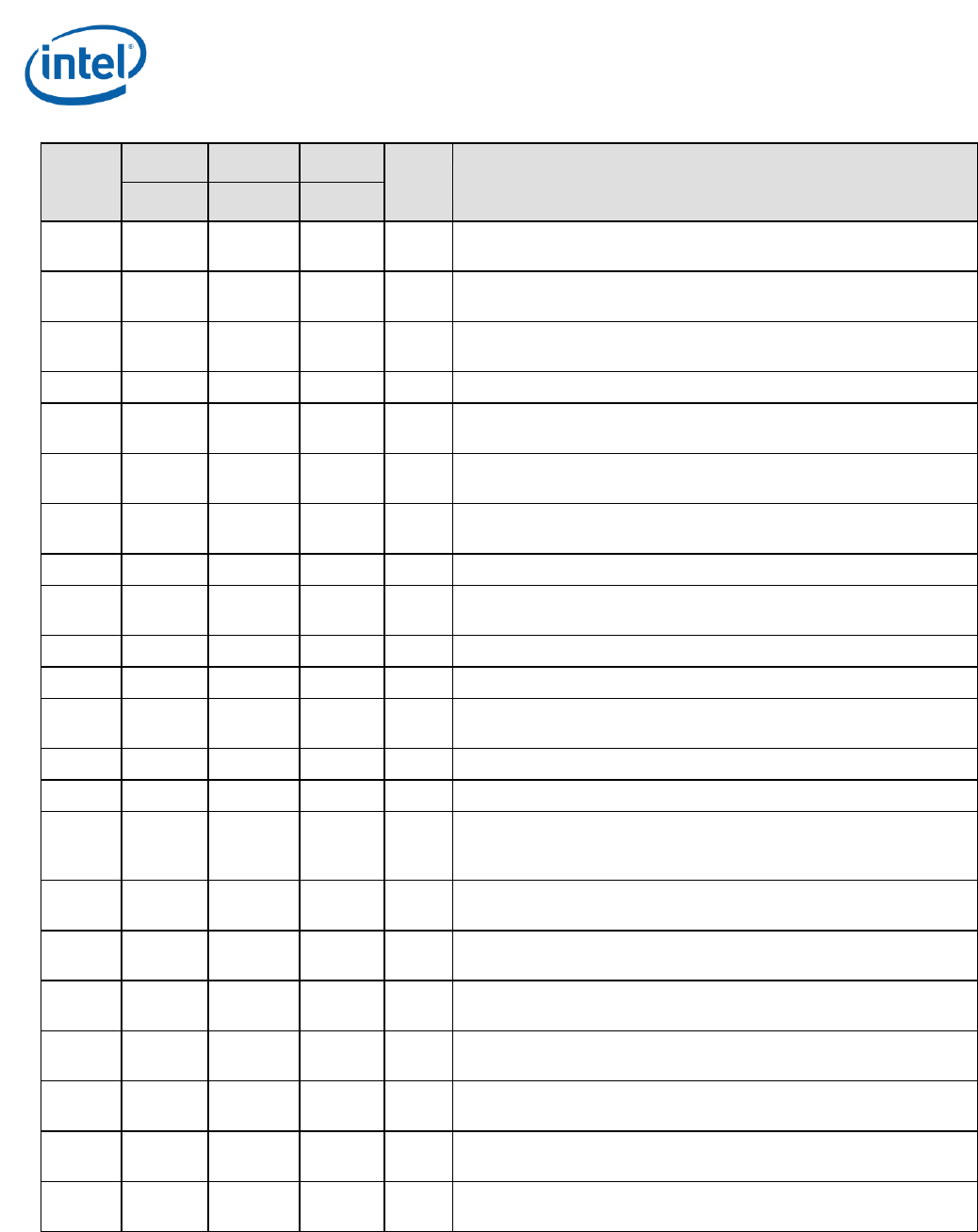

Summary Tables of Changes

32 Specification Update

Number

Stepping

Stepping

Stepping

Plans

ERRATA

E-1

M-1

G-2

AH60

X

X

X

No Fix

LBR, BTS, BTM May Report a Wrong Address when an

Exception/Interrupt Occurs in 64-bit Mode

AH61

X

X

X

No Fix

A Thermal Interrupt Is Not Generated when the Current

Temperature Is Invalid

AH62

X

X

X

No Fix

CMPSB, LODSB, or SCASB in 64-bit Mode with Count Greater or

Equal to 2

48

May Terminate Early

AH63

Removed Erratum

AH64

X

X

X

No Fix

Returning to Real Mode from SMM with EFLAGS.VM Set May Result

in Unpredictable System Behavior

AH65

Fixed

VMLAUNCH/VMRESUME May Not Fail When VMCS Is Programmed

to Cause VM Exit to Return to a Different Mode

AH66

X

X

X

No Fix

IRET under Certain Conditions May Cause an Unexpected

Alignment Check Exception

AH67

X

X

X

No Fix

Performance Monitoring Event FP_ASSIST May Not Be Accurate

AH68

Fixed

CPL-Qualified BTS May Report Incorrect Branch-From Instruction

Address

AH69

Fixed

PEBS Does Not Always Differentiate Between CPL-Qualified Events

AH70

X

X

X

No Fix

PMI May Be Delayed to Next PEBS Event

AH71

Fixed

PEBS Buffer Overflow Status Will Not Be Indicated Unless

IA32_DEBUGCTL[12] Is Set

AH72

X

X

X

No Fix

The BS Flag in DR6 May Be Set for Non-Single-Step #DB Exception

AH73

X

X

X

No Fix

An Asynchronous MCE during a Far Transfer May Corrupt ESP

AH74

Fixed

In Single-Stepping on Branches Mode, the BS Bit in the Pending-

Debug-Exceptions Field of the Guest State Area will be Incorrectly

Set by VM Exit on a MOV to CR8 Instruction

AH75

X

X

X

No Fix

B0-B3 Bits in DR6 May Not Be Properly Cleared after Code

Breakpoint

AH76

X

X

X

No Fix

BTM/BTS Branch-From Instruction Address May Be Incorrect for

Software Interrupts

AH77

Fixed

REP Store Instructions in a Specific Situation May Cause the

Processor to Hang

AH78

X

X

X

No Fix

Performance Monitor SSE Retired Instructions May Return

Incorrect Values

AH79

X

X

X

No Fix

Performance Monitoring Events for L1 and L2 Miss May Not Be

Accurate

AH80

X

X

X

No Fix

Store to WT Memory Data May Be Seen in Wrong Order by Two

Subsequent Loads

AH81

X

X

X

No Fix

A MOV Instruction from CR8 Register with 16 Bit Operand Size Will

Leave Bits 63:16 of the Destination Register Unmodified

- Including Intel 1

- Specification Update 2

- Contents 3

- Revision History 4

- 6 Specification Update 6

- Preface 7

- Nomenclature 8

- Specification Update 9 9

- Identification Information 10

- Table 3. Intel 13

- 945 Express Chipset Family 13

- Component Markings 13

- 14 Specification Update 14

- Table 2. Intel 14

- 965 Express Chipset Family 14

- 16 Specification Update 16

- Table 1. Intel 17

- Celeron 17

- 18 Specification Update 18

- Summary Tables of Changes 19

- Specification Update 21 21

- Errata for Intel 22

- 24 Specification Update 24

- 26 Specification Update 26

- 28 Specification Update 28

- Based on Mobile Intel 29

- 30 Specification Update 30

- 32 Specification Update 32

- 34 Specification Update 34

- 38 Specification Update 38

- May Terminate Early 38

- 40 Specification Update 40

- Specification Update 43 43

- Specification Update 45 45

- Not Be Accurate 46

- Specification 47

- Address Translations 47

- Specification Update 49 49

- Specification Update 51 51

- Invocation 52

- Specification Update 53 53

- Be Incorrect 54

- Specification Update 55 55

- Specification Update 57 57

- Accurate 59

- Specification Update 61 61

- Specification Update 63 63

- Shootdown 65

- Specification Update 67 67

- Address 68

- IA32_DEBUGCTL[12] Is Set 69

- Software Interrupts 71

- Specification Update 73 73

- Specification Update 75 75

- Specification Update 77 77

- Specification Update 79 79

- Instructions as Branches 81

- Signaled 82

- Information 83

- AH108. Overlap of an Intel 84

- VM Exit 84

- Count Some Transitions 85

- Memory-Ordering Violations 86

- Specification Update 87 87

- Shutdown 88

- Specification Update 89 89

- 90 Specification Update 90

- Erratum Affecting Only Intel 91

- Core™2 Duo Mobile 91

- Processors on Mobile Intel 91

- Be Able to Enter Intel 92

- Enhanced Deeper Sleep 92

- AH6P Activation of Intel 93

- Dynamic 93

- Specification Changes 94

- Specification Update 95 95

- Specification Clarifications 96

- Documentation Changes 97

(100 strony)

(100 strony)

Komentarze do niniejszej Instrukcji