Intel LE80537GF0414M Arkusz Danych Strona 33

- Strona / 97

- Spis treści

- BOOKMARKI

Oceniono. / 5. Na podstawie oceny klientów

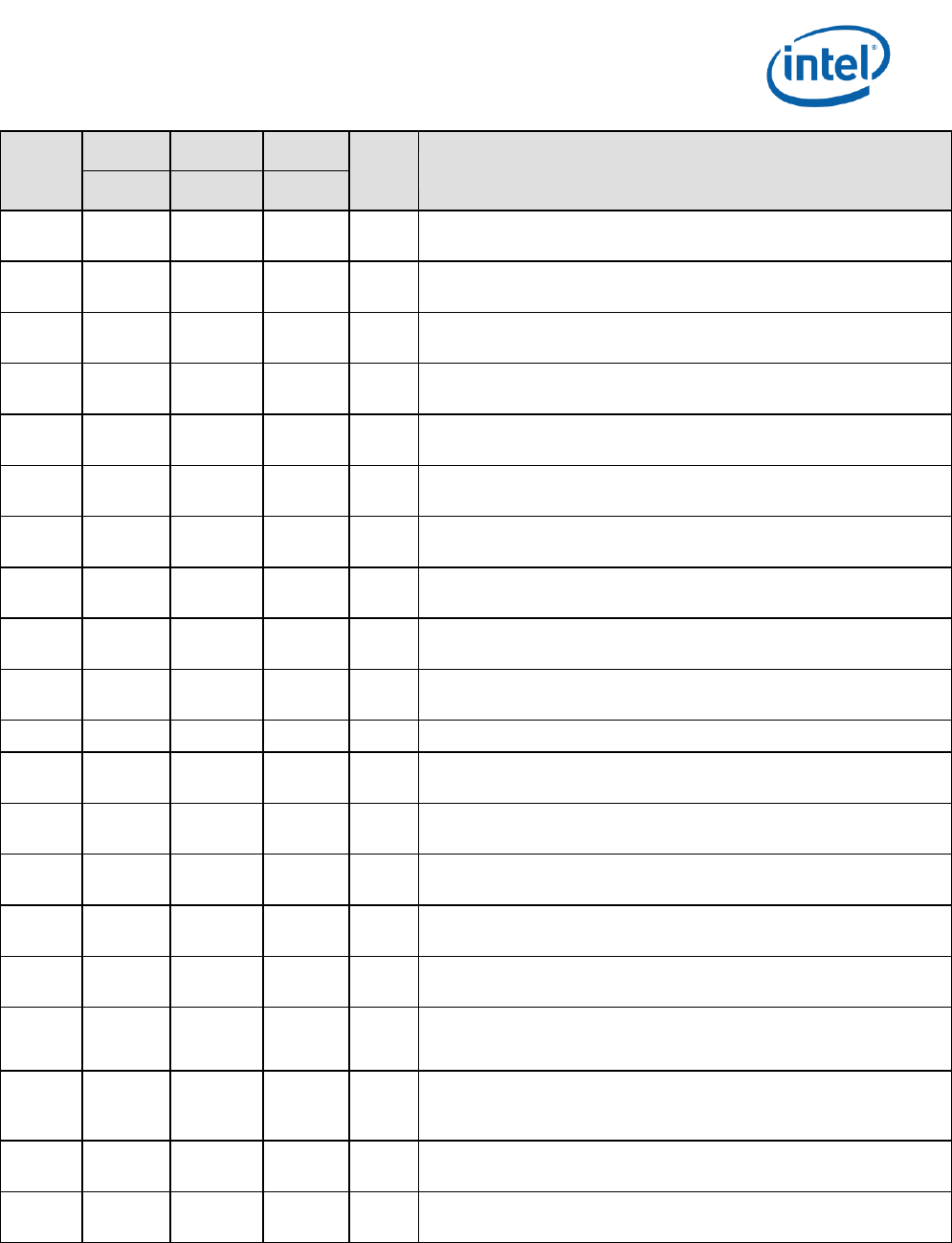

Summary Tables of Changes

Specification Update 33

Number

Stepping

Stepping

Stepping

Plans

ERRATA

E-1

M-1

G-2

AH82

Fixed

Debug Register May Contain Incorrect Information on a MOVSS or

POPSS Instruction followed by SYSRET

AH83

X

X

X

No Fix

Single Step Interrupts with Floating Point Exception Pending May

Be Mishandled

AH84

X

X

X

No Fix

Non-Temporal Data Store May Be Observed in Wrong Program

Order

AH85

X

X

X

No Fix

Fault on ENTER Instruction May Result in Unexpected Values on

Stack Frame

AH86

X

X

Fixed

CPUID Reports Architectural Performance Monitoring Version 2 is

Supported, When Only Version 1 Capabilities are Available

AH87

X

X

X

No Fix

Unaligned Accesses to Paging Structures May Cause the Processor

to Hang

AH88

X

X

X

No Fix

Microcode Updates Performed During VMX Non-root Operation

Could Result in Unexpected Behavior

AH89

X

X

X

No Fix

INVLPG Operation for Large (2M/4M) Pages May be Incomplete

under Certain Conditions

AH90

X

X

X

No Fix

Page Access Bit May be Set Prior to Signaling a Code Segment

Limit Fault

AH91

X

X

Fixed

Update of Attribute Bits on Page Directories without Immediate

TLB Shootdown May Cause Unexpected Processor Behavior

AH92

Fixed

Invalid Instructions May Lead to Unexpected Behavior

AH93

X

X

X

No Fix

EFLAGS, CR0, CR4 and the EXF4 Signal May be Incorrect after

Shutdown

AH94

Fixed

Performance Monitoring Counter MACRO_INSTS.DECODED May

Not Count Some Decoded Instructions

AH95

X

X

Fixed

The Stack May be Incorrect as a Result of VIP/VIF Check on

SYSEXIT and SYSRET

AH96

X

X

X

No Fix

Performance Monitoring Event SIMD_UOP_TYPE_EXEC.MUL is

Counted Incorrectly for PMULUDQ Instruction

AH97

X

X

X

No Fix

Storage of PEBS Record Delayed Following Execution of MOV SS or

STI

AH98

X

X

X

No Fix

Updating Code Page Directory Attributes without TLB Invalidation

May Result in Improper Handling of Code #PF

AH99

X

X

Fixed

Performance Monitoring Event CPU_CLK_UNHALTED.REF May Not

Count Clock Cycles According to the Processors Operating

Frequency

AH100

X

X

X

Plan Fix

Store Ordering May be Incorrect between WC and WP Memory

Types

AH101

Fixed

(E)CX May Get Incorrectly Updated When Performing Fast String

REP STOS With Large Data Structures

- Including Intel 1

- Specification Update 2

- Contents 3

- Revision History 4

- 6 Specification Update 6

- Preface 7

- Nomenclature 8

- Specification Update 9 9

- Identification Information 10

- Table 3. Intel 13

- 945 Express Chipset Family 13

- Component Markings 13

- 14 Specification Update 14

- Table 2. Intel 14

- 965 Express Chipset Family 14

- 16 Specification Update 16

- Table 1. Intel 17

- Celeron 17

- 18 Specification Update 18

- Summary Tables of Changes 19

- Specification Update 21 21

- Errata for Intel 22

- 24 Specification Update 24

- 26 Specification Update 26

- 28 Specification Update 28

- Based on Mobile Intel 29

- 30 Specification Update 30

- 32 Specification Update 32

- 34 Specification Update 34

- 38 Specification Update 38

- May Terminate Early 38

- 40 Specification Update 40

- Specification Update 43 43

- Specification Update 45 45

- Not Be Accurate 46

- Specification 47

- Address Translations 47

- Specification Update 49 49

- Specification Update 51 51

- Invocation 52

- Specification Update 53 53

- Be Incorrect 54

- Specification Update 55 55

- Specification Update 57 57

- Accurate 59

- Specification Update 61 61

- Specification Update 63 63

- Shootdown 65

- Specification Update 67 67

- Address 68

- IA32_DEBUGCTL[12] Is Set 69

- Software Interrupts 71

- Specification Update 73 73

- Specification Update 75 75

- Specification Update 77 77

- Specification Update 79 79

- Instructions as Branches 81

- Signaled 82

- Information 83

- AH108. Overlap of an Intel 84

- VM Exit 84

- Count Some Transitions 85

- Memory-Ordering Violations 86

- Specification Update 87 87

- Shutdown 88

- Specification Update 89 89

- 90 Specification Update 90

- Erratum Affecting Only Intel 91

- Core™2 Duo Mobile 91

- Processors on Mobile Intel 91

- Be Able to Enter Intel 92

- Enhanced Deeper Sleep 92

- AH6P Activation of Intel 93

- Dynamic 93

- Specification Changes 94

- Specification Update 95 95

- Specification Clarifications 96

- Documentation Changes 97

(100 strony)

(100 strony)

Komentarze do niniejszej Instrukcji