Intel 80526KZ667256 Arkusz Danych Strona 96

- Strona / 103

- Spis treści

- BOOKMARKI

Oceniono. / 5. Na podstawie oceny klientów

PENTIUM® III XEON™ PROCESSOR AT 600 MHz to 1 GHz with 256KB L2 Cache

APPENDIX

96

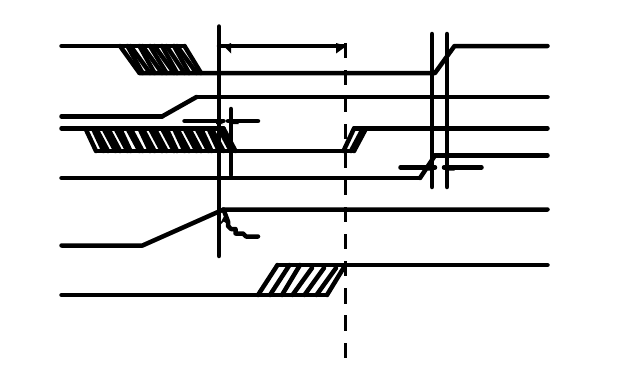

OCVR_OK

Vout (OCVR)

Vin (OCVR)

90% of Vin

Nominal

2.8/5/12V

VCC_CPU

RESET#

VRM_PWRGD

CPU_PWR_GD

1 mS

13mS

0.5 mS (max)

Figure 41. PWRGD Relationship at Power-On

NOTES:

1. VCC_CORE must be applied to the OCVR input before OCVR_OK can become valid (even though it could be pulled high if the

VCC_SMB supply is turned on, see figure 41.

2. The OCVR_OK signal is not guaranteed to be valid until 0.5 mS (max) after Vin to the OCVR reaches 90% of it’s nominal value.

3. Vin is the input to the OCVR (VCC_CORE).

4. Vout is the output from the OCVR (VCC_CPU).

- 1 GHz with 256KB L2 Cache 1

- 1. INTRODUCTION 6

- TERMINOLOGY 7

- 2. TERMINOLOGY 7

- 2.2 References 8

- 3. ELECTRICAL SPECIFICATIONS 9

- 3.1 System Bus and VREF 9

- 3.2 Power and Ground Pins 9

- 3.3 Decoupling Guidelines 10

- ELECTRICAL SPECIFICATIONS 11

- Compatibility 11

- Final Ratio Final Ratio 11

- 3.5 Voltage Identification 12

- 3.7 System Bus Signal Groups 14

- 3.9 Maximum Ratings 16

- Figure 5. Valid Delay Timings 28

- 4. SIGNAL QUALITY 31

- SIGNAL QUALITY 32

- 5. PROCESSOR FEATURES 39

- PROCESSOR FEATURES 40

- 6.1 Thermal Specifications 53

- THERMAL SPECIFICATIONS 54

- with 0° Angle Attachment 57

- with 90° Angle Attachment 57

- 7. MECHANICAL SPECIFICATIONS 58

- MECHANICAL SPECIFICATIONS 59

- 7.1 Weight 62

- 8. INTEGRATION TOOLS 74

- 8.1 In-Target Probe (ITP) 74

- WITH COMPONENT KEEP OUT AREA 75

- PROJECTION 75

- INTEGRATION TOOLS 76

- 9.1 Introduction 82

- 9.2 Mechanical Specifications 82

- 9.3 Thermal Specifications 85

- 10. APPENDIX 89

- Processor 97

- APPENDIX 100

- 10.2 Signal Summaries 101

(34 strony)

(34 strony)

Komentarze do niniejszej Instrukcji